|

Circuit-Level Monitors for Power, Performance, Aging and ReliabilityThis project aims at developing hardware components of the software-driven variability solutions proposed in the Expedition. The hardware outcomes will provide data about, and mechanisms to cope with, the underlying variations including aging, temporal variation, process, and temperature. We seek compact, accurate, and in many cases in situ, sensing techniques to enable software better visibility into the technology platform. Publications: "Crosstalk-aware PWM-based on-chip links with self-calibration in 65nm CMOS," J-S. Seo, D. Blaauw, and D. Sylvester. IEEE Journal on Solid-State Circuits, 05-12-11"A Confidence-Driven Model for Error-Resilient Computing," C-H Chen, Y Kim, Z Zhang, D Blaauw and D Sylvester, U of Michigan, Ann Arbor; H Naeimi and S Sandhu, Intel. Proc. Design, Automation & Test in Europe (DATE\'11), 03-17-11 "Active learning framework for post-silicon variation extraction and test cost reduction," C. Zhuo, K. Agarwal, D. Sylvester, and D. Blaauw. Proc. IEEE/ACM International Conference on Computer-Aided Design 2010, pp. 508-515, 11-11-10 "Dynamic NBTI management using a 45nm multi-degradation sensor," P. Singh, E. Karl, D. Sylvester, and D. Blaauw. Proc. IEEE Custom Integrated Circuits Conference 2010, 09-21-10 Milestones: Tapeout with ARM Cortex M3 along with the SynROs in IBM 45SOI in March 2011. Plans/Outlook: We await silicon results. The simulation results look very promising.

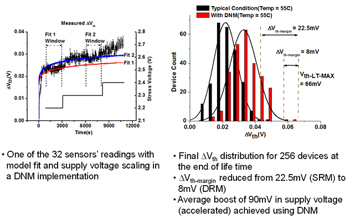

Details of dynamic NBTI management using a subset (32) of compact BTI sensors to predict the wearout of a different set of sensors (224, serving the role of “circuit under test” for this experiment). The left figure shows the measured data of a representative sensor and the fit to the data used to extrapolate to end of lifetime and make decisions on maximum voltage allowed (staircase data inset). At right is the resulting distributions of degradation in the full set of 256 sensors including results without voltage boosting (black) and with boosting (red) to enhance performance by ~10% in this case while preserving lifetime in all sensors given the bound of 66mV maximum DVth. Category: Measurement / Modeling Design Tools / Testing Micro-Architecture / Compilers Campus:

UCLA UMich

People: PIs: Dennis Sylvester (UMich), Puneet Gupta (UCLA); Graduate Students: Dave Fick (UMich), Liangzhen Lai (UCLA), Tuck-Bon Chan (UCLA, now at UCSD) Awards: Intel/CICC Student Scholarship Award, “Dynamic NBTI management using a 45nm multi-degradation sensor” (http://blaauw.eecs.umich.edu/getFile.php?id=426&sid=b7c408d25fe797e9f741afd322f5faef)

|

|

Circuit-Level Monitors for Power, Performance, Aging and Reliability

|