|

Abstractions for Representing Software-Visible Manifestations of Hardware VariationsOur team is investigating abstractions for representing software-visible manifestations of hardware variations at the microarchitectural and architectural/operating system layers, and software for opportunistically exploiting variability using compiler-generated code, and run-time operating system services. Publications: "E-RoC: Embedded Raids-on-Chip for Low Power Distributed Dynamically Managed Reliable Memories," L.A.D. Bathen and N.D. Dutt, UC Irvine. Proc., IEEE/ACM 2011 Design, Automation and Test in Europe, 03-18-11Milestones: Work completed: Luis Bathen has implemented a prototype E-RoC (Embedded Raids-on-Chip) simulation platform for chip multi-processors (CMPs) deploying distributed scratch-pad memories (SPM) with a shared bus architecture. Preliminary simulation experiments on multimedia benchmarks running on a CMP architecture with distributed SPMs have shown that E-RoC’s fully distributed redundant reliable memory subsystem reduces on-chip memory power consumption by up to 85% and latency up to 61% over traditional reliability approaches that use parity/cyclic hybrids for error checking and correction. Plans/Outlook: Two collaborative opportunities are being pursued with the larger Expeditions team:

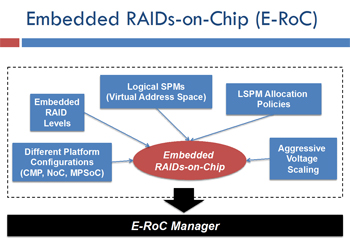

Concept of Embedded RAIDs-on-Chip (E-RoC). E-RoC is composed of eight mutually dependent components (A through I) that are used to create a customized E-RoC Manager for the specific settings of each component. (See Publications) Category: Micro-Architecture / Compilers Runtime Support Campus:

UC Irvine UIUC

People: PIs: Nikil Dutt and Alex Nicolau (UC Irvine), Rakesh Kumar (UIUC); Graduate Students: Luis A.D. Bathen, Arup Chakraborty, and Marco Cesarano

|

|

Abstractions for Representing Software-Visible Manifestations of Hardware Variations

|