|

Imprecise Computation for Energy SavingsThe goal of this project is to study injection of functional errors (by logic changes) as opposed to parametric errors via voltage overscaling to save power for applications which are error tolerant. First goal is to propose alternative multiplier architectures for this purpose. Publications: "Trading Accuracy for Power with an Underdesigned Multiplier Architecture," P. Kulkarni, P. Gupta and M. Ercegovac. Proc., IEEE/ACM International Conference on VLSI Design, 03-31-11Plans/Outlook: Depending on finding an interested student, we plan to extend the idea to other arithmetic units and logic in general; try out the approach on a FPGA (where the tradeoffs would differ).

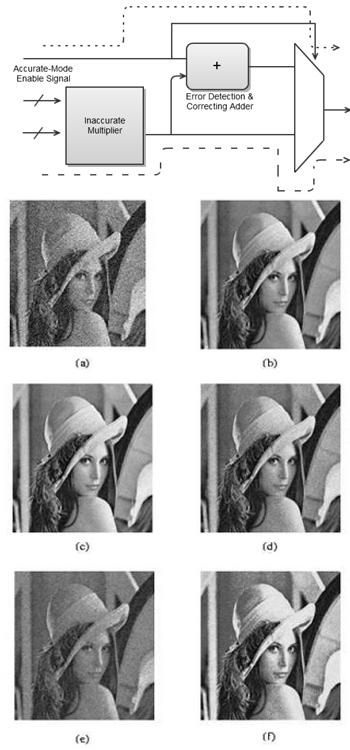

(Top) Illustration of accurate mode extension; the upper path is for accurate operation while the lower path is for inaccurate operation; (bottom) Image sharpening: (a) original blurred image; (b) enhanced using accurate multiplier; (c) by inaccurate multiplier, power reduction 41.5%, SNR: 20.365dB; (d) voltage over-scaling for 30% power reduction, SNR: 9.16dB; (e) voltage over-scaling for 50% power reduction, SNR: 2.64dB; (f) by introducing errors via the adder-tree, SNR : 7.3dB Category: Micro-Architecture / Compilers Campus:

UCLA

People: PI: Puneet Gupta; Graduate Student: Parag Kulkarni (now at Altera Inc.)

|

|

Imprecise Computation for Energy Savings

|